# A CAD Methodology for Optimizing Transistor Current and Sizing in Analog CMOS Design

Kelvin Yuk EEC214 Current

# Contents

- I. Transistor-level Design and Optimization Methodology

- II. Tradeoffs in Analog CMOS Circuit Performance with respect to inversion

- MOS Operating Plane

- Sizing and parameter relationships

- MOS DC bias and small signal parameters

- Gain and Bandwidth

- DC Mismatch and Gate-Referred Flicker Noise

- III. CAD Tool Implementation and Example

- IV. Conclusions

### Transistor-level design methodology

- Design methodology

- Select a circuit topology

- Select desired performance specifications

- Computerized optimization to select MOS currents and sizings to meet specs

- Can also simulate topology over a range of currents and sizings and explore tradeoffs

- Transistor-level design methodology

- Allows designer to pre-select near-optimal drain currents and sizings for any circuit

- Considers transconductance  $g_{\rm m}$  and output conductance  $g_{\rm ds}$

- Permits design in weak, moderate, or strong inversion

# MOS Inversion Coefficient

- Traditionally, degrees of design freedom are drain current I<sub>D</sub>, channel width W and channel length L.

- Here, degrees of freedom are drain current  $I_D$ , channel length L and inversion level IC, which is a normalized measure of  $I_D$  describing level of channel inversion.

$$IC = \frac{I_D}{2n\mu C_{OX} (W/L) U_T^2}$$

$$n = (COX + VDEP)/COX,$$

$$U_T = kT/q$$

• Weak inversion: IC < 0.1 ( $V_{GS} - V_T \sim = -72mV$ ) Moderate inversion center: IC = 1.0 ( $V_{GS} - V_T \sim = 40mV$ ) Strong inversion: IC > 10 ( $V_{GS} - V_T \sim = 220mV$ )

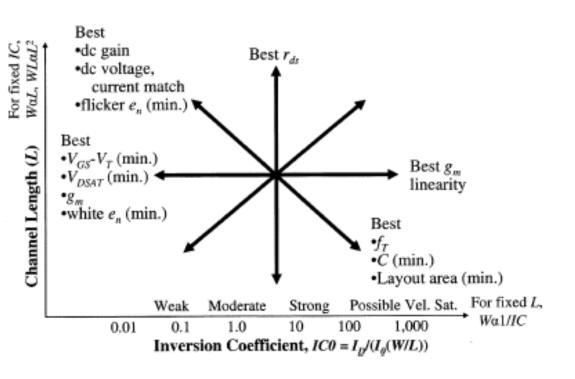

#### Performance Tradeoffs – MOS Operating Plane

$$IC_{0} = \frac{I_{D}}{2n_{0}\mu_{0}C_{OX}(W/L)U_{T}^{2}} = \frac{I_{D}}{I_{0}(W/L)}$$

- Best C and intrinsic-gain bandwidth f<sub>T</sub> at high IC, small L.

- Opposite for intrinsic gain, dc match, flicker noise.

- V<sub>DSAT</sub>, g<sub>m</sub>, white noise optimal at low IC.

- g<sub>m</sub> linearity best at high IC

- Fix n0 at moderate inversion, mu0 at low field value.

- I0 is technology current

# MOS Sizing Relationships

- If IC is increased (I<sub>D</sub> and L fixed), (W/L) ratio, W, gate area (and C<sub>OX</sub>), decrease inversely with increasing IC.

- If L is increased (I<sub>D</sub> and IC fixed), W increases directly with L to maintain (W/L) ratio. Since W increases, gate area (and C<sub>OX</sub>) increases as square of increasing L.

- If I<sub>D</sub> increased (IC and L fixed), (W/L) ratio, W, and gate area (and C<sub>OX</sub>) increase directly with increasing I<sub>D</sub>.

MOS DC Bias Voltage and Small-Signal Parameter Relationships

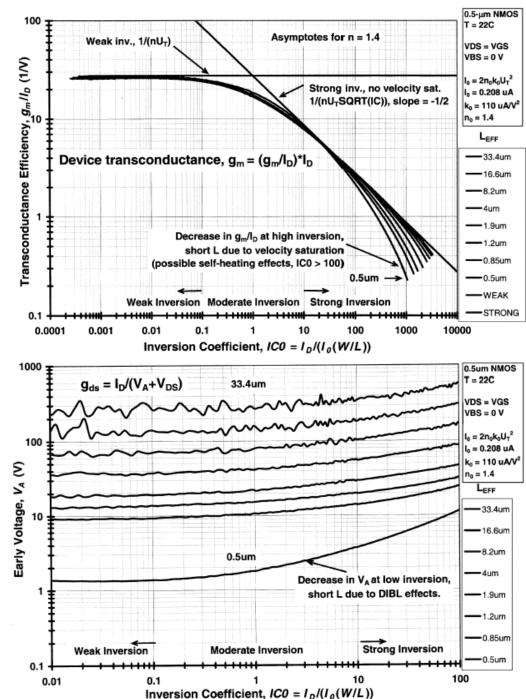

- Weak/moderate inversion best for maximizing g<sub>m</sub> and minimizing white noise

- Long channel length L results in higher V<sub>A</sub> and subsequently lower output conductance g<sub>ds</sub> → higher r<sub>ds</sub>

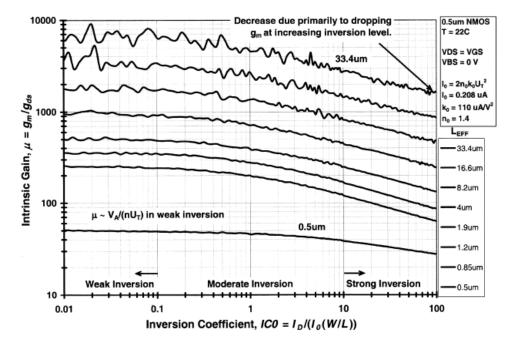

### Gain and Bandwidth

- Intrinsic gain is highest at weak inversion with long channel length L

- Intrinsic gain is lowest at strong inversion with short channel length L

TABLE III MOS GAIN AND BANDWIDTH RELATIONSHIPS

| Parameter<br>(W and L are effective dimensions.)                                                                                                                                                            | $IC_0 \uparrow$<br>L, $I_D$ fixed                               | $L \uparrow IC_0, I_D$ fixed | $I_D \uparrow$<br>$IC_0, L$ fixed |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------|-----------------------------------|

| Intrinsic Gain <sup>1,2</sup> :                                                                                                                                                                             | Unchanged,<br>W.I. <sup>2</sup>                                 | $\uparrow \propto L^{1,2}$   | Unchanged                         |

| $A_{VI} = \frac{g_m}{g_{ds}} = \frac{I_D(g_m / I_D)}{I_D(g_{ds} / I_D)} = \frac{I_D / V_{gm}}{\approx I_D / V_A} \approx \frac{V_A}{V_{gm}}$ $\approx \frac{VAL \cdot L}{nU_T(\sqrt{0.25 + IC} + 0.5)}$ (1) | $\downarrow \propto \frac{1}{\sqrt{IC}},$<br>S.L <sup>1,2</sup> |                              |                                   |

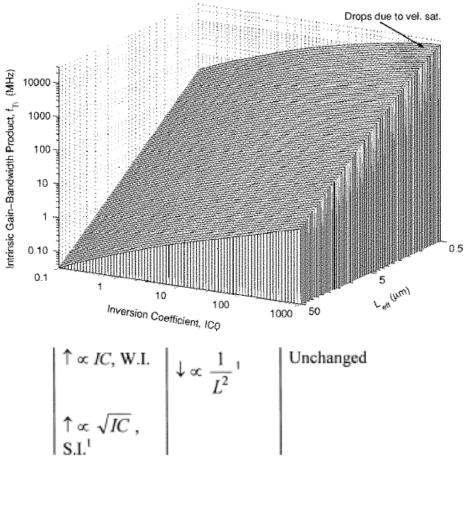

### Gain and Bandwidth cont'd

- Best BW at high IC0, short L

- Velocity saturation at high IC0, short L, causing BW to limit

$$f_{Ti} = \frac{g_m}{2\pi (C_{gsi} + C_{gbi})}$$

$$= \frac{\frac{IC_0}{\sqrt{0.25 + IC} + 0.5} \cdot \frac{I_0}{nU_T}}{2\pi (C_{gsi} + C_{gbi})L^2 C_{OX}}$$

$$C'_{gsi} = \frac{C_{gsi}}{WLC_{OX}} = \frac{0}{3}, \frac{1}{3}, \frac{2}{3}, \text{ for } W.I., M.I., S.I.$$

$$C'_{gbi} = \frac{C_{gbi}}{WLC_{OX}} = \left[\frac{3}{3}, \frac{2}{3}, \frac{1}{3}\right] \frac{n}{n-1},$$

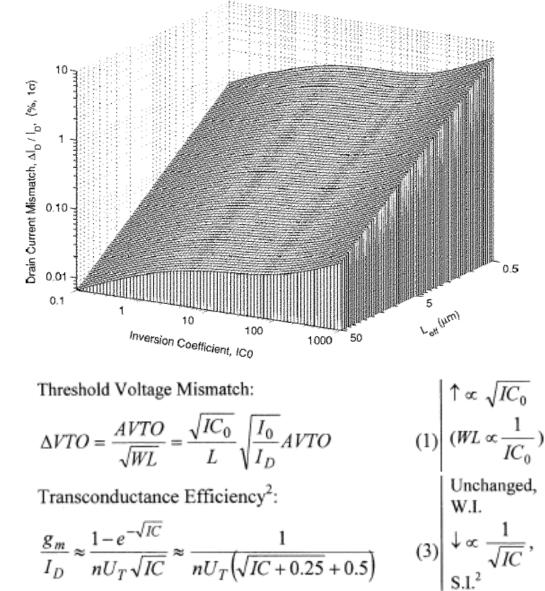

### DC Mismatch and Gate-Referred Flicker Noise

- Since mismatch dependant on I<sub>D</sub>.

Normalization of ID offset required for different ID

- I<sub>D</sub> current mismatch optimized at long L, low IC.

- In strong inversion, ID mismatch almost independent of IC

#### DC Mismatch and Flicker Noise

- I<sub>D</sub> mismatch due to threshold voltage mismatch

- DC mismatch and input-referred flicker noise voltage are minimized by maximizing gate area.

- Operating in weak IC and long L is also where max MOS gain is obtained

TABLE IV MOS DC MISMATCH AND GATE-REFERRED FLICKER NOISE RELATIONSHIPS

| Parameter                                                                                                                                                                                                                       |         | $IC \uparrow L, I_D$ fixed     | $L \uparrow IC, I_D$ fixed                                                          | $I_D \uparrow$<br>IC, L fixed       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------|-------------------------------------------------------------------------------------|-------------------------------------|

| Threshold Voltage Mismatch:                                                                                                                                                                                                     |         | $\uparrow \propto \sqrt{IC_0}$ | $\downarrow \propto \frac{1}{2}$                                                    | ↓ oc                                |

| $\Delta VTO = \frac{AVTO}{\sqrt{WL}} = \frac{\sqrt{IC_0}}{L} \sqrt{\frac{I_0}{I_D}} AVTO \tag{6}$                                                                                                                               | 1)      | $(WL \propto \frac{1}{IC_0})$  | $ \begin{array}{l} \downarrow \propto \frac{1}{L} \\ (WL \propto L^2) \end{array} $ | $\sqrt{I_D}$<br>(WL $\propto I_D$ ) |

| Transconductance Factor Mismatch:<br>(generally negligible for $IC < 100$ )                                                                                                                                                     |         |                                |                                                                                     |                                     |

| $\Delta KP = \frac{AKP}{\sqrt{WL}} = \frac{\sqrt{IC_0}}{L} \sqrt{\frac{I_0}{I_D}} AKP \qquad ($                                                                                                                                 | (2)     |                                |                                                                                     |                                     |

| Body-Effect Factor Mismatch:<br>(present only for nonzero $V_{BS}$ )                                                                                                                                                            |         |                                |                                                                                     |                                     |

| AGAMMA VICo Io                                                                                                                                                                                                                  | (3)     |                                |                                                                                     |                                     |

| Gate-Referred Flicker Noise Voltage:                                                                                                                                                                                            |         |                                |                                                                                     |                                     |

| $S_{V flic  \text{ker}}^{1/2}(f) = \sqrt{\frac{K_F}{C_{OX}^2 W L f^{AF}}} = \frac{1}{\sqrt{WL}} \sqrt{\frac{K_F}{C_{OX}^2 f^{AF}}}$ $= \frac{\sqrt{IC_0}}{L} \sqrt{\frac{I_0}{I_D}} \bullet \sqrt{\frac{K_F}{C_{OX}^2 f^{AF}}}$ | (4)     |                                |                                                                                     |                                     |

| $(\frac{V}{\sqrt{H}})$                                                                                                                                                                                                          | =)<br>z |                                |                                                                                     |                                     |

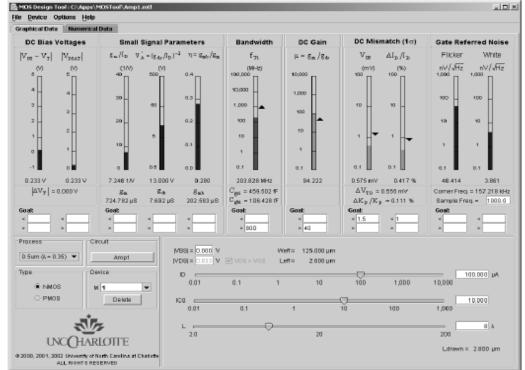

# CAD Design Tool

- MOS circuit performance evaluated by

- a) Linkage to commercial SPICE-like simulator that can run EKV and BSIM3 models

- b) Linkage to custom MOS model equations which may modify existing MOS model

- c) Linkage to arrays of measured MOS data

- User interface allows designer to select design parameters as well as desired performance specs and dynamically display tradeoffs using colored bar graphs.

# CAD Tool Example

| Design | n Inputs        | 8    | Result | Ilting Circuit Performance |            |                 |                 |                 |                  |                 |               |         |

|--------|-----------------|------|--------|----------------------------|------------|-----------------|-----------------|-----------------|------------------|-----------------|---------------|---------|

|        |                 | Lay- | Min.   | Small signal               |            |                 | Band-           | DC mismatch     |                  | Gate referred   |               |         |

|        |                 |      | out    | V <sub>DS</sub>            | Parameters |                 |                 | width           | (1σ)             |                 | noise voltage |         |

| ID     | IC <sub>0</sub> | L    | W      | VDSAT                      | gm         | g <sub>ds</sub> | A <sub>Vi</sub> | f <sub>Ti</sub> | $\Delta I_D/I_D$ | $\Delta V_{GS}$ | white         | flick.1 |

| μΑ     |                 | μm   | μm     | V                          | μS μS V/V  |                 | MHz             | %               | mV               | nV/(Hz)1/2      |               |         |

| 100    | 10              | 0.5  | 24     | 0.25                       | 657        | 40.0            | 16.4            | 4,997           | 1.98             | 3.02            | 4.06          | 251.8   |

| 100    | 10              | 1.2  | 58     | 0.24                       | 705        | 16.7            | 42.3            | 931             | 0.88             | 1.25            | 3.92          | 104.9   |

| 100    | 10              | 2.6  | 126    | 0.23                       | 725        | 7.69            | 94.2            | 204             | 0.42             | 0.58            | 3.86          | 48.4    |

|        |                 |      |        |                            |            |                 |                 |                 |                  |                 |               |         |

| 100    | 1               | 1.2  | 578    | 0.14                       | 1670       | 16.7            | 100             | 286             | 0.64             | 0.38            | 2.54          | 33.2    |

| 100    | 10              | 1.2  | 58     | 0.24                       | 705        | 16.7            | 42.3            | 931             | 0.88             | 1.25            | 3.92          | 104.9   |

| 100    | 100             | 1.2  | 5.8    | 0.79                       | 223        | 16.7            | 13.4            | 2,714           | 1.14             | 5.11            | 6.96          | 331.7   |

ILLUSTRATION OF NMOS SIZING OPTIMIZATIO

- NMOS xtr at ID = 100uA, 0.5um CMOS process

- Intrinsic voltage gain Avi > 40 V/V lacksquareIntrinsic bandwidth fTi > 800MHz DC current mismatch < 1% (1 sigma) (current mirror) DC voltage mismatch < 1.5 mV(1 sigma) (diff. pair)

- Short L, BW met, Avi, mismatch not met.

- Long L, Avi, mismatch met, BW not met.

### Conclusions

- Transistor level design methodology can produce optimal drain current and sizing for use in any analog circuit topology using ID, IC and L to find W

- Exploring the performance of a transistor operating at different inversion levels can benefit circuit performance and expand design options

- Every MOS xtr operates in the MOS operating plane from which tradeoffs between a variety of performance criteria can be explored

- CAD tools can be designed to implement advanced behavior of MOS transistors and optimize them based on the relationships established with inversion level as a design parameter

- Device optimizations can be done before circuit simulations to reduce trial and error simulations while considering high order effects

Reference:

A CAD Methodology for Optimizing Transistor Current and Sizing in Analog CMOS Design, D.M. Binkley, C.E. Hopper, S.D. Tucker, B.C. Moss, J.M. Rochelle, D.P. Foty

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol.22, No. 2, February 2003