By Kelvin Yuk and Jackie Xue

Written: Dec 4, 2002

Nowadays, there is a million of Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFET) in digital, analog, and mixed-signals circuits, and noise in transistors has limited the minimum signal level that a circuit can process with acceptable quality. In other words, noise lowers the signal to noise ratio (SNR) and that will introduce more data bit errors in transmission system. In general, there are three types of noise; they are thermal, shot, and flicker noise. This paper will describe the phenomenon of flicker noise in MOSFET. Flicker noise is also called 1/f noise because the power spectral density of the flicker noise is inversely proportional to the frequency f (-10 dB/decade) [1].

By so far, there does not exist a universal model to describe the physical origins of the flicker noise that is agreed by everyone. However, there are two models exist that are agreed by most individual. These two models are the Carrier-density fluctuation model (number fluctuations) and the mobility fluctuation model. The number fluctuations model originally proposed by McWhorter, the flicker noise is attributed to the random trapping and detrapping processes of charges in the oxide traps near the Si-SiO2 interface [2]. Many dangling bonds appear when the silicon crystal reaches an end at the interface and this will give rise to extra energy states. Charge carriers at the interface are randomly trapped and later released by such energy states, introducing flicker noise in the drain current.

The mobility fluctuation model, on the other hand, consider the flicker noise as a result of the fluctuation in bulk mobility based on Hooge’s empirical relation for the spectral density of flicker noise in a homogeneous sample:

where I is the mean current flowing through the sample, SI is the spectral density of the noise in the current, Ntotal is the total number of free carriers in the sample, and aH, known as Hooge’s parameter, is an empirical constant with a value of about 2 ´ 10-3 [2]. When equation 1 is applied to MOSFET, it predicts that the input referred flicker noise power is proportional to (Vg – Vth)Cox-1.

Besides the number fluctuations and mobility fluctuation models, Hung, Ko, Hu, and Cheng have put these two models together into one model and they called it “A Unified Model for the Flicker Noise in MOSFET”. The reason they put the number and mobility fluctuations models together is the measured noise power in MOSFET’s has a more complicated dependence on the gate bias and oxide thickness than the number or mobility fluctuation model predicts [2]. In the unified model, when the carrier density is uniform along the channel the total drain current noise power is

where g is the attenuation coefficient of the electron wave function in the oxide, m is the carrier mobility, Nt(Efn) is the oxide trap levels around quasi-Fermi level, k is the Boltzmann’s constant, T is the temperature, f is the frequency, N is the number of channel carriers per unit area, a is the scattering coefficient, Id is the total drain current, W is the width of the transistor, and L is the length of the transistor.

Since flicker noise is related to the trapping and detrapping of carriers along the interface of the gate oxide, improvements in fabrication can reduce these traps that cause current fluctuations. One method that has shown to reduce flicker noise in PMOS transistors is a simple cleaning step using ammonia hydrogen peroxide (APM) mixture prior to gate oxidation [3]. The cleaning showed significant noise reduction versus a PMOS with a gate oxide grown immediately after hydrogen fluoride etching (HF-finished). The cleaning affected neither gate oxide capacitance nor any significant device characteristics but showed decreases in noise level as well as interface trap density. The results of the cleaning showed an average reduction of noise of –14dBV2/Hz in the PMOS transistor but showed no significant noise reduction in NMOS transistors. The interface trap density of APM-finished PMOS transistors was 3.02 x 1011 cm-2 versus 6.47 x 1011 cm-2 for an HF-finished PMOS. This reduction in interface traps and noise level show the benefit of this additional cleaning step.

Though improvements in processing can lead to good noise reduction, there also exist techniques that allow the circuit designer to improve the noise performance of a MOS circuit. Many circuit design noise reduction techniques like operating in weak inversion, reducing drift current, and reducing phase noise using phase locked loops, though, have either drawbacks in performance or may only reduce the effect of flicker noise at low frequency [1]. Flicker noise affects low frequency operation but can also appear at high frequencies in circuits like mixers, VCOs and frequency dividers where the noise is upconverted to different harmonics. Switched biasing is robust in reducing flicker noise because it preserves circuit performance and tackles the problem of upconverted noise.

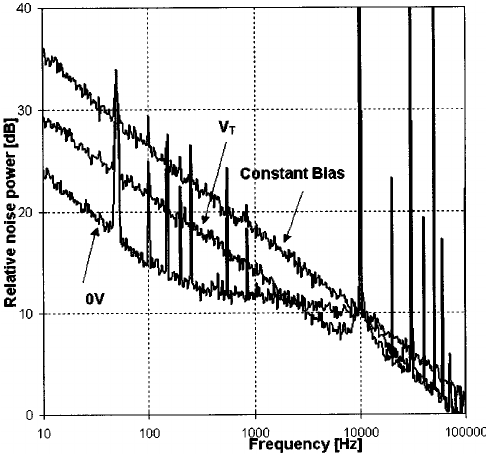

Switched biasing involves cycling the operation mode of the transistor from saturation to accumulation or near accumulation mode by periodically biasing the gate between two different voltages. This is implemented by biasing the gate of a MOS between two voltage levels: VGS_on (VGS >VT and VDS > VDSsat) and VGS_off (VGS <= VT and VDS > VDSsat). Since flicker noise is greater in strong inversion than in weak inversion or accumulation, powering the transistor off avoids excessive flicker noise. In a single transistor experiment, it was found that the value of VGS_off affects the attenuation of flicker noise. When VGS_off was equal to VT, the transistor showed a noise reduction of 6dB whereas a VGS_off of 0V showed a noise reduction of 8dB. To show how the method can benefit a more practical circuit, switched biasing was implemented on a coupled sawtooth oscillator. The transistor producing the dominant 1/f noise of the circuit was identified and on-off functionality was added to it. The signal used to drive the switched biasing transistor was derived from the oscillator itself, so no additional signals were needed. The results of this experiment showed a reduction of 14dB in the 1/f noise spectral density.

Although switched biasing shows promise in reducing the intrinsic noise of the transistor, applying it may be difficult in many circuits. In the sawtooth oscillator example, the signal used to alternate the operation mode of the current source was wired from the oscillator itself. However, not all circuits will have a signal available to switch bias the noise producing MOS between on and off states. Periodically switching the MOS on and off may require additional hardware or an additional square wave signal to produce the switched biasing effect. The cost of implementing the additional hardware may drastically increase design time and area use. Therefore the necessity of low noise in the application will determine the feasibility of implementing switched biasing.

In applications that demand low-noise performance, the accurate modeling of flicker noise becomes a vital part in understanding the behavior of low-noise circuits. The unified model is more complete than the individual mobility fluctuation and number fluctuation models because it encompasses qualities of both. Since the exact mechanism for flicker noise is not fully understood, the unified model can give insight from both perspectives on how the flicker noise affects transistor performance. When noise mechanisms are identified, the reduction of noise in circuits also becomes more feasible. There are many techniques both process and circuit design related that show promise. Although some of these noise reduction methods can increase design time and hardware costs, it may be worth considering where good noise performance is needed.

References

[1] Eric A. M. Klumperink, Sander L. J. Gierkink, Arnoud P. van der Wel, and Bram Nauta, “Reducing MOSFET 1/f Noise and Power Consumption by Switched Biasing,” IEEE Journal of Solid-State Circuits, vol. 35, no. 7, July 2000.

[2] Kwok K. Hung, Ping K. Ko, Chenming Hu, and Yiu C. Cheng, “A Unified Model for the Flicker Noise in Metal-Oxide-Semiconductor Field-Effect Transistors,” IEEE Transactions on Electron Devices, vol. 37, no. 3, March 1990.

[3] Masato Toita, Tomohiro Akaboshi, and Hisaya Imai, “1/f Noise Reduction in PMOSFETs by an Additional Preoxidation Cleaning With an Ammonia Hydrogen Peroxide Mixture,” IEEE Electron Device Letters, vol. 22, no. 11, November 2001.